高性能系統(tǒng)設(shè)計師在滿足關(guān)鍵時序余量的同時要力爭獲得更高性能,而存儲器接口設(shè)計則是一項艱巨挑戰(zhàn)。雙倍數(shù)據(jù)速率SDRAM和4倍數(shù)據(jù)速率SDRAM都采用源同步接口來把數(shù)據(jù)和時鐘(或選通脈沖)由發(fā)射器傳送到接收器。接收器接口內(nèi)部利用時鐘來鎖存數(shù)據(jù),此舉可消除接口控制問題(例如在存儲器和FPGA間的信號傳遞時間),但也為設(shè)計師帶來了必須解決的新挑戰(zhàn)。

關(guān)鍵問題之一就是如何滿足各種讀取數(shù)據(jù)捕捉需求以實現(xiàn)高速接口。隨著數(shù)據(jù)有效窗越來越小,該問題也益發(fā)重要;同時,更具挑戰(zhàn)性的問題是,如何讓接收到的時鐘與數(shù)據(jù)中心對準(zhǔn)。

基于FPGA、ASIC和ASSP控制器的設(shè)計所采用的傳統(tǒng)方法是使用鎖相環(huán)或延遲鎖定環(huán)電路,以保證在源時鐘和用于捕捉數(shù)據(jù)的時鐘間具有固定的相移或延時。該方法的一個明顯缺點是延時是固定的單一值,且在整個設(shè)計周期是預(yù)設(shè)定好的。但在實際系統(tǒng)中,由到不同存儲器器件的不同布線、FPGA間的變異以及工藝、電壓和溫度等系統(tǒng)條件所引發(fā)的難以預(yù)測的變化很容易帶來偏差,因此,預(yù)先設(shè)定的相移是不準(zhǔn)確的。

現(xiàn)在,領(lǐng)先FPGA供應(yīng)商提供的新的硅特性、以及硬件經(jīng)過驗證的參考設(shè)計已克服了

這些挑戰(zhàn)。此外,工程師還必須遵循一些基本規(guī)則以縮短設(shè)計周期。

應(yīng)該利用最新的FPGA硅特性來構(gòu)建接口。這樣做將減少FPGA邏輯資源使用,優(yōu)化功耗并提高時序余裕。分辨率75 ps的可調(diào)輸入延時時拍等I/O硅特性可支持精準(zhǔn)的時鐘到數(shù)據(jù)對中。

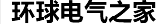

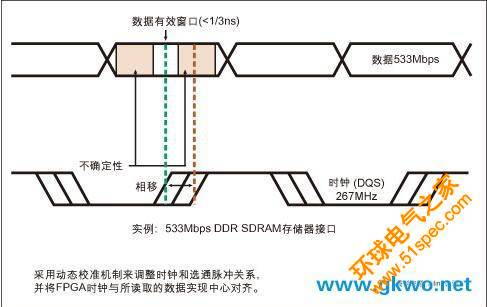

采用動態(tài)校準(zhǔn)機制來調(diào)整時鐘和選通脈沖的關(guān)系并將FPGA時鐘對準(zhǔn)讀取數(shù)據(jù)的中心。這種方案可提供運行時調(diào)整以補償設(shè)計過程中無法考慮到的所有系統(tǒng)變異。

采用領(lǐng)先FPGA供應(yīng)商提供的硬件經(jīng)過驗證的參考設(shè)計。用戶在自己的定制設(shè)計中,可把參考設(shè)計作為起點,從而節(jié)省寶貴的時間和資源。

根據(jù)PCB和FPGA設(shè)計,驗證同時切換輸出的一致性。采用具有電源管腳均勻分布的新FPGA封裝,通過有效改善信號返回電流路徑降低SSO噪聲。該技術(shù)可支持更寬的數(shù)據(jù)總線。

運行Ibis仿真以確保信號質(zhì)量。此舉將有助于為不同信號選擇和調(diào)整終接端子。在分析中,利用實際PCB布局來運行仿真,以綜合串?dāng)_、去耦、終止和線跡配置的影響。圖1采用動態(tài)校準(zhǔn)機制來調(diào)整時鐘和選通脈沖關(guān)系,并將FPGA時鐘與所讀取的數(shù)據(jù)實現(xiàn)中心對齊。

圖1 動態(tài)校準(zhǔn)機脈沖關(guān)系

避免:在讀周期中,采用固定相移延時使時鐘或選通脈沖對中數(shù)據(jù)有效窗。當(dāng)數(shù)據(jù)速率很高時,由于在設(shè)計期間無法考慮到的工藝、電壓和溫度等系統(tǒng)變異,這么做可能減小設(shè)計余裕。

跳過功能性和布局-布線后仿真步驟不執(zhí)行。這些步驟所花的時間往往可在硬件調(diào)試期間得到幾倍的回報。另外,當(dāng)需要最佳性能時,布局后仿真是接口調(diào)試的良好工具。

任意選取管腳,選擇時僅憑借經(jīng)驗和常識。一般來說,應(yīng)該把數(shù)據(jù)位集中在一起,并保持在一或兩個時鐘區(qū)內(nèi),這樣可以產(chǎn)生好的結(jié)果。另外,還要考慮FPGA裸片內(nèi)的接口映射,它應(yīng)靠近實現(xiàn)接口的區(qū)域,以減小內(nèi)部布線延時。 ; 假定驅(qū)動器的阻抗為0歐姆。總線上負(fù)載越大意味著對信號完整性約束的要求越嚴(yán)格。就深接口來說,考慮利用幾個帶寄存器的DIMM來達(dá)到期望的存儲器深度(帶寄存器DIMM的地址網(wǎng)絡(luò)的負(fù)載僅為1,而無緩沖器的DIMM的負(fù)載是18)。

PCB布局中,在通過接口的返回路徑上出現(xiàn)中斷和障礙物。中斷將使返回電流的路徑更長,并會在系統(tǒng)中產(chǎn)生有害噪聲。