隨著各種電路和芯片的性能(速度、集成度等)不斷提高,尤其是在軍事、航空航天等用途中對可靠性的要求往往是第一位的,人們對于系統(tǒng)的可靠性方面的要求日益增加,這對電路系統(tǒng)的設(shè)計和制造都提出了嚴(yán)格的目標(biāo)要求。

存儲器是電路系統(tǒng)中最常用的器件之一,采用大規(guī)模集成電路存儲芯片構(gòu)成。實際統(tǒng)計表明,存儲器在太空應(yīng)用中的主要錯誤是由瞬態(tài)錯誤(也叫單個事件擾動,SEU)所引起的一位錯[1]或者相關(guān)多位錯,而隨機(jī)獨(dú)立的多位錯誤極少。半導(dǎo)體存儲器的錯誤大體上分為硬錯誤和軟錯誤,其中主要為軟錯誤。硬錯誤所表現(xiàn)的現(xiàn)象是在某個或某些位置上,存取數(shù)據(jù)重復(fù)地出現(xiàn)錯誤。出現(xiàn)這種現(xiàn)象的原因是一個或幾個存儲單元出現(xiàn)故障。軟錯誤主要是由α粒子引起的。存儲器芯片的材料中含有微量放射性元素,他們會間斷地釋放α粒子。這些粒子以相當(dāng)大的能量沖擊存儲電容,改變其電荷,從而引起存儲數(shù)據(jù)的錯誤。引起軟錯誤的另一原因是噪聲干擾。同時在太空環(huán)境下,在帶電粒子足夠能量撞擊下,存儲器的存儲單元中的位發(fā)生翻轉(zhuǎn)從而產(chǎn)生SEU錯誤[2]。本文設(shè)計實現(xiàn)了用CPLD技術(shù)和糾檢錯芯片對存儲器進(jìn)行容錯,大大提高了系統(tǒng)的可靠性。下面是具體容錯存儲器和門警電路的設(shè)計。

1 檢錯與糾錯原理

常用的能檢測2位錯同時能糾正1位錯(簡稱糾一檢二,SEC-DED[3、4])的糾錯碼有擴(kuò)展?jié)h明碼(ExtendedHammingCode)和最佳奇權(quán)碼(Optimal 他們的最小碼距都為4,兩者有相似之處,如冗余度一樣,對于數(shù)據(jù)位數(shù)k,校驗位數(shù)r應(yīng)滿足2r-1≥k+r。當(dāng)k=16時,r=6,數(shù)據(jù)位長增加1倍,校驗位數(shù)只需增加1位,編碼效率較高。另外從來源上講,兩者分別是漢明碼的擴(kuò)展碼和截短碼,也有資料稱最佳奇權(quán)碼為修正漢明碼(ModifiedHammingCode)。文獻(xiàn)[4]介紹了SEC-DED和SEC-AUED)碼的編解碼理論。從性能上看最佳奇權(quán)碼比擴(kuò)展?jié)h明碼更為優(yōu)越,前者在糾檢錯能力方面也優(yōu)于后者,他的3位錯誤的誤糾概率低于后者,而4位錯誤的檢測概率高于后者,最重要的是他便于硬件實現(xiàn),故應(yīng)用的最多,本文采用最佳奇權(quán)碼。

首先構(gòu)造最佳奇權(quán)碼的校驗矩陣即H矩陣,最佳奇權(quán)碼的H矩陣應(yīng)滿足:

(1)每列含有奇數(shù)個1,且無相同列。

(2)總的1的個數(shù)少,所以校驗位、伴隨式生成表達(dá)式中的半加項數(shù)少,從而生成邏輯所需的半加器少,可以節(jié)約器材、降低成本和提高可靠性。

(3)每行中1的個數(shù)盡量相等或接近某個平均值,這種決定生成邏輯及其級數(shù)的一致性,不僅譯碼速度快,同時線路勻稱。

應(yīng)用中采用(13,8,4)最佳奇權(quán)碼,數(shù)據(jù)碼為(d7d6d5d4d3d2d1d0),校驗碼為(c4c3c2c1c0),P矩陣和編碼規(guī)則分別為:

P矩陣和編碼規(guī)則分別為

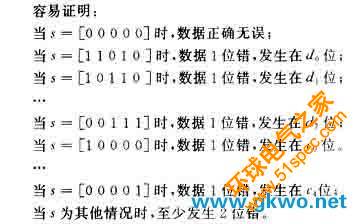

譯碼時把數(shù)據(jù)再次編碼所得到的新校驗位與原校驗位模2加,便得到伴隨式S,由其可判別錯誤類型:

(1)若S=0,則認(rèn)為沒有錯誤;

(2)若S≠0,且S含有奇數(shù)個1,則認(rèn)為產(chǎn)生了單位錯;若S≠0,且S含有偶數(shù)個1,則認(rèn)為產(chǎn)生了2位錯。

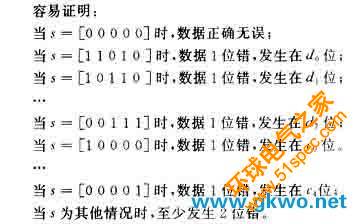

因此,錯誤圖樣S=[s0 s1 s2 s3 s4]與產(chǎn)生的錯誤一一對應(yīng),從而實現(xiàn)糾一檢二功能。

2 存儲器容錯芯片設(shè)計實現(xiàn)

2.1 存儲器設(shè)計實現(xiàn)方案

(1)備份行(或列)方案

這種方案是在存儲芯片的設(shè)計與制造過程中增加若干備份的行(或列)。在芯片測試時,若發(fā)現(xiàn)失效的行(或列),則通過激光(或電學(xué))的處理,用備份行(或列)去代

替。此方法的優(yōu)點(diǎn)是設(shè)計簡單,管芯面積增加較少,電路速度沒有損失。但是,他需要增加某些測試與修正實效行(或列)的工藝環(huán)節(jié),更重要的弱點(diǎn)是這種方案僅適用于RAM,不能用于ROM。

(2)糾錯編碼方案

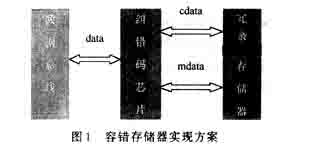

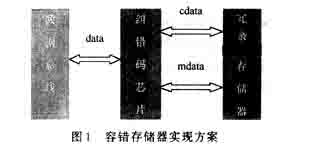

這種方案是在存儲芯片內(nèi)部采用糾錯編碼,自動檢測并糾正錯誤。此方案不需要額外的測試和糾正錯誤等工藝環(huán)節(jié),除提高成品率外,還對可靠性有明顯改進(jìn)。這種方案最突出的優(yōu)點(diǎn)是特別適合ROM;在對速度要求不高的情況下也可用于RAM。他的主要缺點(diǎn)在于要占用額外的芯片面積,同時因編譯碼而影響芯片整個的工作速度。將用于存儲器系統(tǒng)級的糾錯編碼等容錯技術(shù)引入存儲器芯片內(nèi)部,是提高存儲芯片成品率和可靠性的有效措施。例如服務(wù)器中使用的ECC內(nèi)存就采用了此技術(shù)。本文的容錯存儲器采用糾錯碼方案,其實現(xiàn)框圖如圖1所示。

2.2 糾檢錯電路設(shè)計

糾檢錯電路必須配合CPU的讀寫時序進(jìn)行工作,可以將CPU的時序分為讀周期和寫周期。在寫周期時,總線通過糾錯電路直接將數(shù)據(jù)寫入到存儲器,同時數(shù)據(jù)通過糾錯電路產(chǎn)生5b校驗碼寫入到冗余存儲器。讀周期時分成2步,第1步從存儲器和冗余存儲器分別讀取數(shù)據(jù)和校驗位數(shù)據(jù)送入糾錯電路鎖存;第2步進(jìn)行檢錯,如果沒有錯誤直接將數(shù)據(jù)送出到數(shù)據(jù)總線,有2位錯產(chǎn)生中斷進(jìn)行處理,有1位錯對數(shù)據(jù)進(jìn)行糾錯并送入數(shù)據(jù)總線。因需要的是正確數(shù)據(jù),如果是校驗位出錯則不進(jìn)行任何處理,直接輸出正確數(shù)據(jù)。

2.3 電路輸入輸出設(shè)計

RD,WR,CLK為CPU輸入到糾檢錯信號,通過控制電路產(chǎn)生芯片內(nèi)控制信號。在寫信號時,DB[7..0]從數(shù)據(jù)總線輸入,通過鎖存以后經(jīng)過三態(tài)控制(Santai模塊)寫入到存儲器,同時數(shù)據(jù)通過校驗碼產(chǎn)生模塊(Paritygen)產(chǎn)生5b校驗碼,通過三態(tài)控制寫入冗余存儲器。讀信號時,存儲器數(shù)據(jù)讀入糾檢錯電路經(jīng)過鎖存后產(chǎn)生5b校驗碼,同時與從冗余存儲器讀入的5b檢驗碼一起通過錯誤圖樣模塊(Errorsample),產(chǎn)生錯誤圖樣。通過錯誤圖樣檢測錯誤,當(dāng)數(shù)據(jù)產(chǎn)生錯誤時通過糾錯模塊(Errorcorrect)糾錯后將正確數(shù)據(jù)輸出到數(shù)據(jù)總線。Errordetec為錯誤狀態(tài)模塊,SEF,DEF為錯誤狀態(tài)信號。0,0時無錯,1,0時1位錯,1,1時2位錯。電路實現(xiàn)的各部分功能模塊如圖2所示。

電路實現(xiàn)的各部分功能模塊

3 仿真及其波形

本文采用Altera公司的CPLD器件EPM7128作為設(shè)計環(huán)境[5],圖3是糾檢錯電路仿真圖形,用CPLD實現(xiàn)糾檢錯電路仿真,圖中118~205ns時從數(shù)據(jù)線上寫入數(shù)據(jù)AA,359~443ns時仿真了讀數(shù)據(jù)時產(chǎn)生1位錯情況,601~692ns時仿真了產(chǎn)生2位錯情況,此時檢測到了2位錯,但是不能糾正。781~863ns時仿真了校驗位產(chǎn)生1位錯時的情況。

糾檢錯電路仿真

4 分析與結(jié)論

本文利用最佳奇權(quán)碼的基本原理設(shè)計的糾錯碼電路可以校正單位錯,檢出2位錯,存儲器不因單位錯而中斷工作,故其平均無故障時間MTBF增大,提高了可靠性。但是糾一檢二碼的新增器材又使MTBF有所下降。

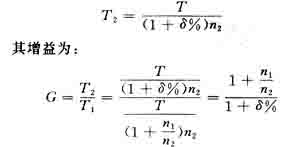

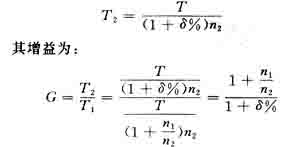

在效率上,設(shè)在時間T內(nèi),發(fā)生1位錯的次數(shù)為n1,發(fā)生2位及多位錯的次數(shù)為n2,采用糾錯碼時,平均無故障時間為T1=T/(n1+n2),采用最佳奇權(quán)碼后,1位錯是可糾的,僅2位及多位錯是不可糾的,作為出錯處理。設(shè)由于采用糾錯碼而增加器材δ%,因而采用最佳奇權(quán)碼后的平均無故障時間為:

采用最佳奇權(quán)碼后的平均無故障時間為

據(jù)資料估計,對于1位錯占整個錯誤的比例對于1位錯占整個錯誤的比例,增益G=4.6~9.3。通過CPLD來實現(xiàn)存儲器的容錯,大大縮短了設(shè)計開發(fā)周期,降低了成本,同時提高了系統(tǒng)的可靠性