當前位置: 首頁 > 工業電子產品 > 其他電子產品 > 開發板,套件,編程器 > 開發板

發布日期:2022-10-14 點擊率:100

射頻電路設計實錄(RF Design Record,簡稱RDR)是無線時代網站推出的系列射頻技術文章,記錄了一款產品的完整設計過程。本文是其中的第四章,ADS仿真。

4. ADS仿真

從本章開始,將進入本產品設計的核心階段。

4.1 PCB板材的選擇

4.1.1 需要考慮的因素

也許很多讀者還不知道的是,PCB板材的選擇是ADS仿真的第一步。理由如下:

4.1.2 常用的射頻PCB板材

常用的射頻板材廠商及其型號如表4-1所示。

表4-1 常用的射頻板材廠商及其型號

| Taconic | |||||||

| 型號 | 頻率 | 介電常數 | 損耗因子 | 型號 | 頻率 | 介電常數 | 損耗因子 |

| HT1.5 | 10GHz | 2.35±0.05 | 0.0025 | 射頻-35 | 1.9GHz | 3.5±0.1 | 0.0025 |

| TLE-95 | 10GHz | 2.95±0.05 | 0.0028 | 射頻-30 | 1.9GHz | 3.0±0.1 | 0.0014 |

| TLX-9 | 10GHz | 2.50±0.04 | 0.0019 | TLY-5 | 10GHz | 2.20±0.02 | 0.0009 |

| TP-32 | 10GHz | 3.20±0.1 | 0.0022 | TSM-30 | 10GHz | 3.0±0.05 | 0.0015 |

| TLT-9 | 1MHZ | 2.50±0.05 | 0.0006 | TLC-32 | 10GHz | 3.20±0.05 | 0.03 |

| Rogers | |||||||

| 型號 | 頻率 | 介電常數 | 損耗因子 | 型號 | 頻率 | 介電常數 | 損耗因子 |

| R04350 | 10GHz | 3.48±0.05 | 0.004 | R04003 | 10GHz | 3.38±0.05 | 0.0027 |

| R04403 | 10GHz | 3.17±0.05 | 0.005 | R03003 | 10GHz | 3.00±0.04 | 0.0013 |

| R03203 | 10GHz | 3.02±0.04 | 0.0016 | RT5880 | 10GHz | 2.20±0.02 | 0.0009 |

| RT5870 | 10GHz | 2.33±0.02 | 0.0012 | ULT2000 | 10GHz | 2.60±0.04 | 0.0022 |

| RT6002 | 10GHz | 2.94±0.04 | 0.0012 | TMM3 | 10GHz | 3.27±0.032 | 0.002 |

| R04233 | 10GHz | 3.33±0.05 | 0.0026 | FLEX3000 | 10GHz | 2.9±0.04 | 0.002 |

| Arlon | |||||||

| 型號 | 頻率 | 介電常數 | 損耗因子 | 型號 | 頻率 | 介電常數 | 損耗因子 |

| DiC1ad527 | 10GHz | 2.60 ± 0.04 | 0.0022 | DiC1ad870 | 10GHz | 2.33±0.02 | 0.0013 |

| DiC1ad880 | 10GHz | 2.20 ± 0.02 | 0.0009 | IsoC1ad 933 | 10GHz | 2.33±0.04 | 0.0016 |

| IsoC1ad917 | 10GHz | 2.20±0.04 | 0.0013 | AD 250 | 10GHz | 2.5 | 0.0018 |

| AD 270 | 10GHz | 2.7 | 0.003 | AD 300 | 10GHz | 3 | 0.003 |

| AD 320 | 10GHz | 3.2 | 0.003 | AD 350 | 10GHz | 3.5 | 0.0018 |

| 25N | 10GHz | 3.38±0.06 | 0.0025 | 25FR | 10GHz | 3.58±0.06 | 0.0035 |

| Getek | |||||||

| 型號 | 頻率 | 介電常數 | 損耗因子 | 型號 | 頻率 | 介電常數 | 損耗因子 |

| RF300B1080 | 10GHz | 3.8 | 0.0074 | RF300B2313 | 10GHz | 3.9 | 0.0074 |

| RF300B7628 | 10GHz | 4.1 | 0.0074 | DS300B7628 | 10GHz | 4.2 | 0.0074 |

| ML200H1080 | 10GHz | 3.3 | 0.009 | ML200K1080 | 10GHz | 3.4 | 0.01 |

| ML200K2116 | 10GHz | 3.5 | 0.01 | RG200K1080 | 10GHz | 3 | 0.003 |

| AD 320 | 10GHz | 3.2 | 0.003 | AD 350 | 10GHz | 3.8 | 0.009 |

| RF300H1080 | 10GHz | 3.3 | 0.006 | DS300H2116 | 10GHz | 3.4 | 0.006 |

| Parknelco | |||||||

| 型號 | 頻率 | 介電常數 | 損耗因子 | 型號 | 頻率 | 介電常數 | 損耗因子 |

| N4000-12 | 10GHz | 3.6 | 0.008 | N4000-12SI | 10GHz | 3.2 | 0.006 |

| N5000 | 10GHz | 3.6 | 0.014 | N7000-1 | 10GHz | 3.8 | 0.016 |

| N7000-2HT | 10GHz | 3.5 | 0.015 | N8000 | 10GHz | 3.5 | 0.011 |

| NY9000 | 10GHz | 2.33 | 0.0011 | NX9000 | 10GHz | 3.2 | 0.0024 |

| NH9000 | 10GHz | 3.5 | 0.003 | N9000 | 10GHz | 3.5 | 0.0055 |

4.1.3 PCB板材的確定

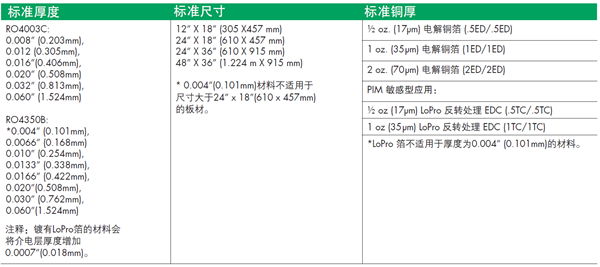

相信很多讀者對于羅杰斯板材都有所耳聞,本人也是如此,與PCB制板廠聯系之后,得知RO4003C與RO4350B都是常備型號。其中RO4003C與RO4350B又分別有幾種不同的規格,如圖4-1。

圖4-1 RO4000系列PCB機械特性

圖4-1 RO4000系列PCB機械特性

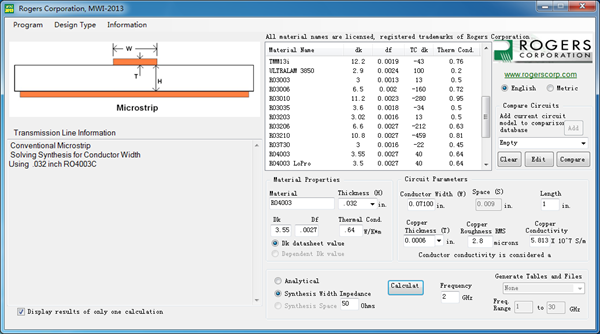

根據前文的討論,本產品使用2層板足以完成全部設計,因此RO4003C的0.813mm板材是比較合適的,0.8mm的板厚強度還是可以的。值得一提的是,羅杰斯官方網站有一款叫做MWI的免費軟件,里面已經內置了Rogers公司的全部板材參數,讀者可自行前往Rogers官方網站下載,也可以在本站下載。

使用MWI計算RO4003C 0.8mm板厚特征阻抗方法如圖4-2所示,可以看到,當特征阻抗控制為50歐姆時,走線寬度為71mil,完全可以滿足LDMOS的饋電要求。

圖4-2 使用MWI計算特征阻抗

4.2 LDMOS末級輸出放大器設計與仿真

這部分的仿真是本章的核心內容。

4.2.1 獲取LDMOS仿真模型

如前所述,本產品使用Freescale的MRF8S26060H作為末級輸出器件,讀者可以自行前往Freescale的官方網站獲取仿真模型,獲取仿真模型的鏈接如下,點擊MRF8S26060H_MDL_ADS后面的“Download”按鈕進行下載。

http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=MRF8S26060H&fpsp=1&tab=Design_Tools_Tab

需要注意的是,僅下載這個模型還不夠,實際仿真時還需要使用另外的一個Model Kit叫做RF_HIGH_POWER_MODEL_ADS_KIT,讀者可以點擊上述鏈接中RF_HIGH_POWER_MODEL_ADS_KIT后面的“Download”按鈕進行下載。

4.2.2 導入LDMOS仿真模型

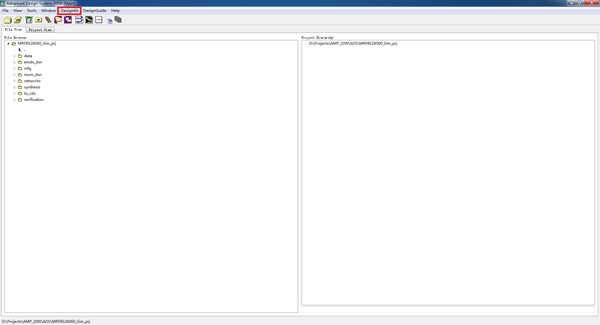

在ADS主界面中點擊DesignKit按鈕,如圖4-3。

圖4-3 點擊DesignKit按鈕

在彈出的Install ADS Design Kit對話框中點擊“Unzip Design Kit Now”按鈕,并在新的對話框中點擊Browse按鈕,選擇剛剛下載得到zip后綴的文件,如圖4-4。

圖4-4 選擇Design Kit

選擇完成后回到Install ADS Design Kit對話框,我們可以看到如圖4-5所示的結果。

圖4-5 已解壓的DesignKit

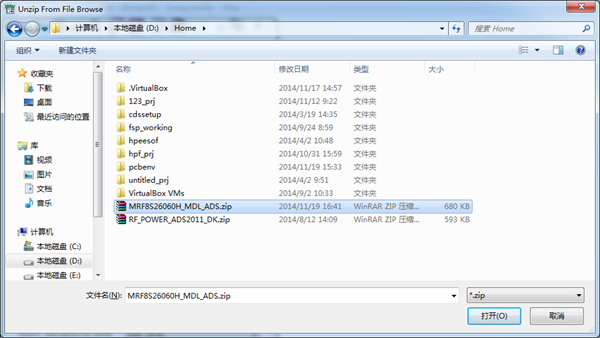

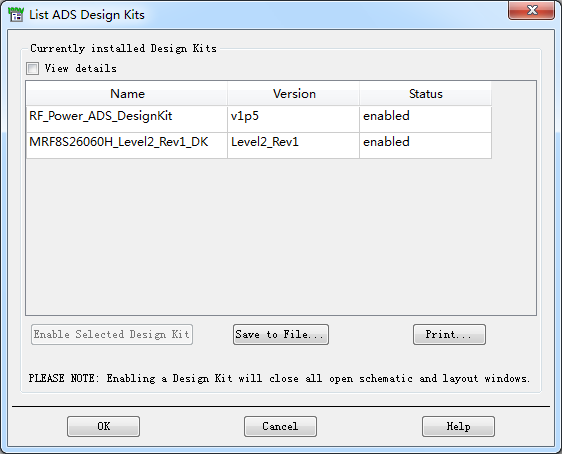

此時點擊OK,即可將MRF8S26060H的模型添加至ADS的庫中。用同樣的方法處理RF_POWER_ADS2011_DK.zip,最后點擊DesignKit?List Design Kits,即可顯示出已安裝的仿真模型,如圖4-6。

圖4-6 List ADS Design Kits

4.2.3 創建仿真工程

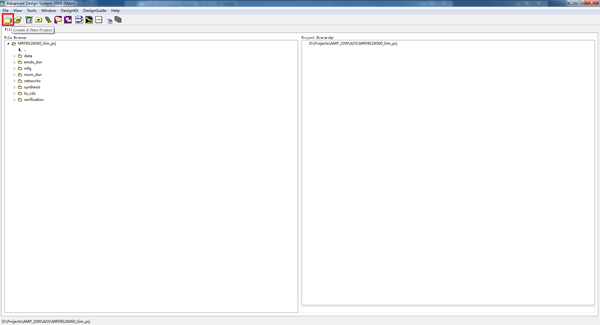

在ADS主界面中點擊“Create A New Project”圖標,開始創建仿真工程,如圖4-7。

圖4-7 創建仿真工程

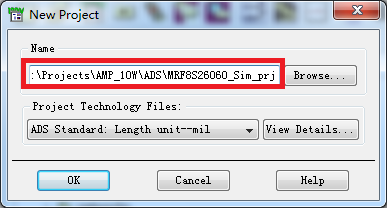

在彈出的對話框中點擊Browse找到希望保存的目錄,在本設計中,選擇了D:’ProjectsAMP_10WADS目錄。在Name欄中文件夾路徑后輸入MRF8S26060_Sim_prj,ADS就完成了名為MRF8S26060_Sim_prj的仿真工程,如圖4-8。此時,ADS會自動彈出一個原理圖繪制窗口。

圖4-8 輸入項目名稱

4.2.4 LDMOS直流仿真

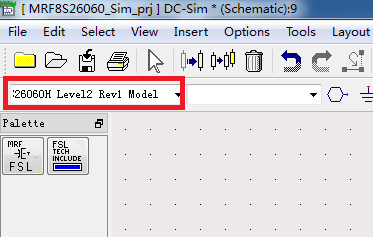

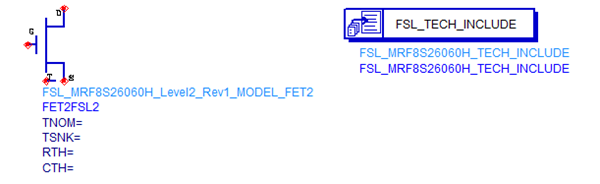

將4.2.3中彈出的原理圖另存為DC-Sim.dsn,在器件庫中選擇Freescale MRF8S26060H Level2 Rev1 Model,如圖4-9所示。

圖4-9 選擇Freescale元器件庫

這時依此點擊出現的兩個圖標,便可以將MRF8S26060H的仿真模型及所涉及到的庫文件放置在原理圖中,如圖4-10。

圖4-10 在原理圖中添加MRF8S26060H

分別選擇Simulation-DC與Probe_Components控制板,添加電流表,PARAMETER SWEEP,DC,DisplayTemplate等控件,并按照如圖4-11的方式連接完成,就得到了直流仿真的原理圖。

圖4-11 直流仿真原理圖

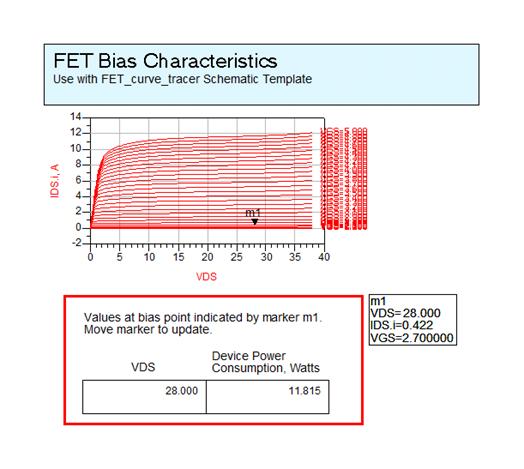

這時可點擊Simulate圖標,可以得到如圖4-12所示的直流仿真結果。可以看到m1處Vds=28V,Vgs=2.7V,Ids=0.422A,這與MRF8S26060H Datasheet中所描述的基本一致。

圖4-12 直流仿真結果

4.2.5 LDMOS負載牽引仿真

負載牽引仿真是極其重要的環節。此處會花費較多篇幅進行講解,在本站的一篇文章中總結了ADS負載牽引仿真中經常遇到的問題及解決辦法,具體可查看https://www.witimes.com/loadpull-design-key-points-ads/。

所謂負載牽引仿真,就是在放大器后面連接一個可變負載,當負載在一定范圍內變化時,測量不同負載對應的不同的輸出功率及PAE,負載牽引仿真的目的就是找到獲得預期輸出功率及PAE時對應的負載值。

4.2.5.1 使用Loadpull仿真模板

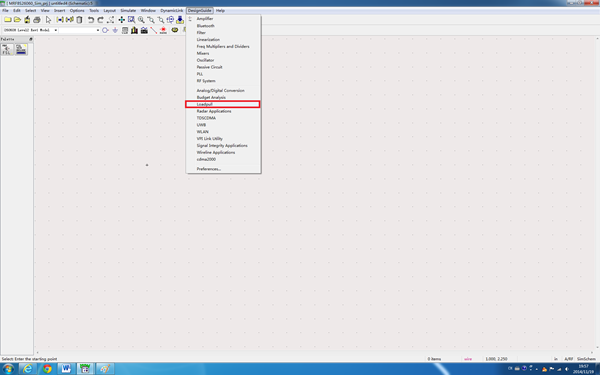

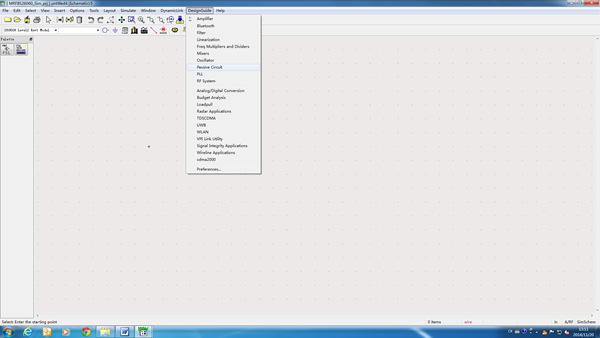

在MRF8S26060_Sim_pr新建一頁原理圖,點擊DesignGuide?Loadpull,如圖4-13所示。

圖4-13 點擊DesignGuide Loadpull

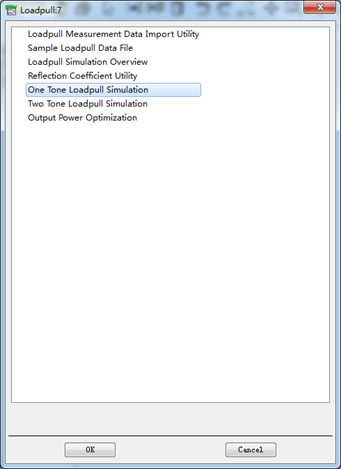

在彈出的對話框中選擇One Tone Loadpull Simulation,即“單音負載牽引仿真”如圖4-14所示。

圖4-14 選擇One Tone Loadpull Simulation

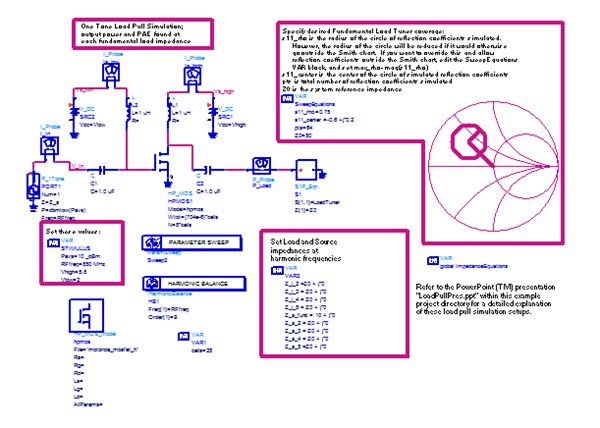

點擊OK,原理圖中會出現ADS中已經設置好的仿真模板,如圖4-15所示。

圖4-15 加載負載牽引仿真模板

4,2,5,2 Loadpull仿真過程

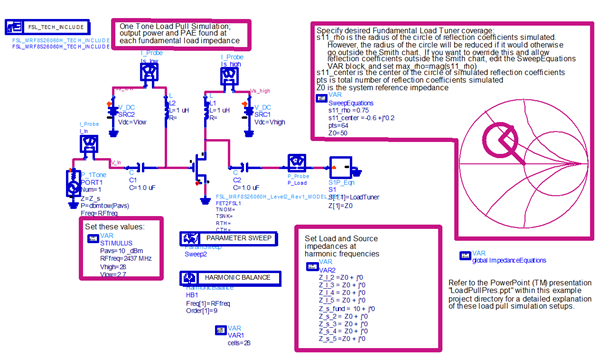

將4.2.5.1原理圖中的默認FET換成MRF8S26060H,并將FSL_MRF8S26060H_TECH_INCLUDE添加至原理圖;將VAR控件中的RFfreq設置為2437MHz,Vhigh即Vds設置為28V,Vlow設置為2.7V,如圖4-16所示。

圖4-16 設置仿真條件

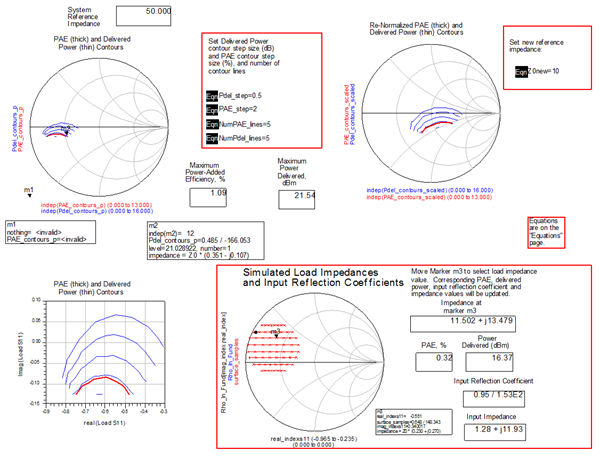

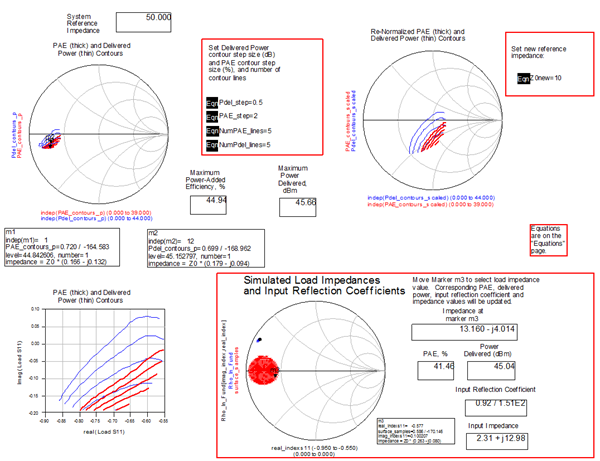

這時點擊Simulate按鈕,ADS便開始仿真過程,稍等片刻,便可以得到如圖4-17所示的仿真結果(仿真結果的模板也是預先設置好的)。可以看到,最大的PAE(附加功率效率)僅為1.09%,最大功率也僅為21.54dBm,增益僅為11.54dB,與理想值差距比較大。

圖4-17 第一次負載牽引仿真結果

將Pavs更改為30dBm,再次仿真,得到如圖4-18所示的仿真結果。可以看到,此時最大PAE已經大幅提升至27.26%,最大功率提升為42.21dBm,增益沒有發生太大變化。其實這個結果是很容易理解的,當輸入至LDMOS的功率較小時,LDMOS自身的靜態功耗比例較大,所以PAE極低;隨著輸入功率的提升,LDMOS消耗的功率極其輸出功率都在上升,但輸出功率上升的更快,LDMOS自身的靜態功耗比例減少,所以PAE大幅提升。

圖4-17 第二次負載仿真結果

雖然在第二次仿真后,PAE已大幅提升,但增益仍達不到要求,這就需要設置SweepEquations中的參數,即調整S11的原點及半徑,調整仿真的范圍。

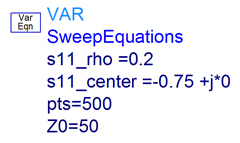

值得注意的是,調整仿真范圍非常容易出現仿真結果不收斂的情況,這個時候讀者就需要按照https://www.witimes.com/loadpull-design-key-points-ads/文中提到的方法。由于文章篇幅的關系,我無法在本文中給出全部的實驗過程,只能給出最終的仿真結果。在最終的仿真參數設定中,SweepEquations中的s11_rho設置為0.2,S11_center=-0.75+j*0,pts=500,同時將pavs設置為33dBm,如圖4-18所示。

圖4-18 最終的仿真參數設定

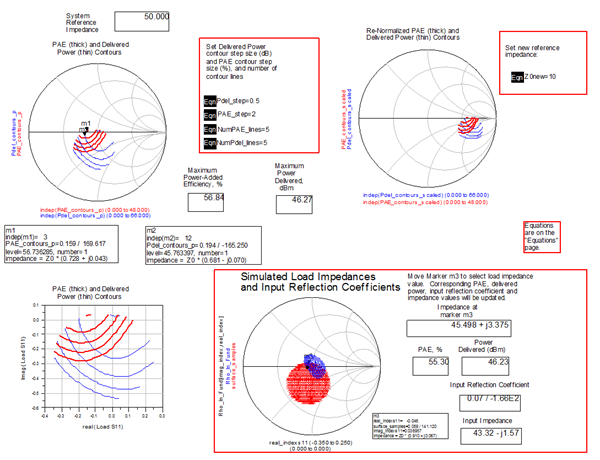

再次仿真,得到如圖4-19所示的結果。可以看到,在m3點處,可以獲得45.04dBm的輸出功率并且對應的PAE為41.46%,很不錯。

圖4-19 第三次負載牽引仿真結果

這時,可以看到當前的負載為13.16-j4.014,輸入阻抗為2.31+j12.98。

4.2.6 LDMOS匹配電路設計與仿真

有了4.2.5中結論,我們就需要為LDMOS構造出13.16-j4.014的負載,當然也可以得知這時LDMOS的輸出阻抗為13.16+j4.014。

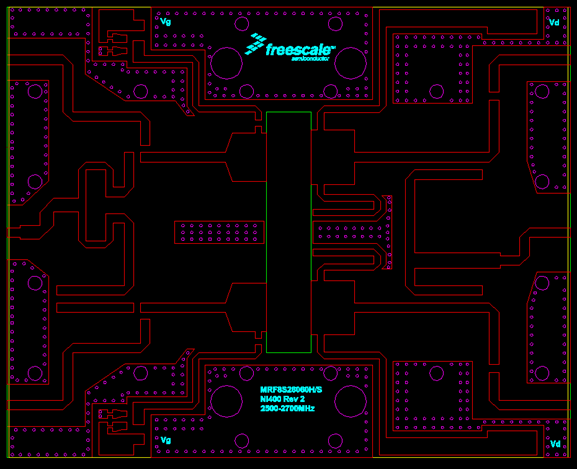

不過,就在這時,本產品的設計工作發生了戲劇性的轉變——Freescale發來了MRF8S26060H的參考設計,由于產品開發時間的限制,能用上Freescale的參考設計無疑是件很好的事情。雖然Freescale發來的參考設計是DXF格式,但是也為設計工作提供了巨大的幫助,參考設計如圖4-20所示。

圖4-20 MRF8S26060參考設計

從結構上看,這是一款Doherty結構的功放,但是每顆LDMOS又可以分別測試,也許這是為了方便客戶評估,但這些不是本設計關心的重點,在本文中僅關心LDMOS的匹配電路。顯而易見的是,LDMOS的偏置電路及Vds均是采用四分之一波長走線的方式,并通過微帶線方式完成匹配。

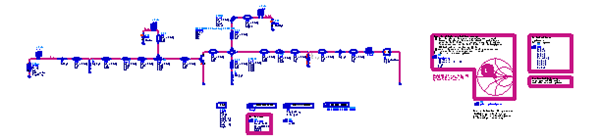

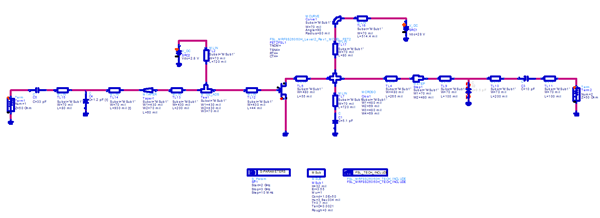

為了最大限度地縮短產品開發周期,我們測量出MRF8S26060H相關的微帶線尺寸,并在ADS中創建新的負載牽引原理圖,如圖4-21所示。此處配圖可能不夠清晰,但后續無線時代會推出PDF高清版,將會配備矢量圖,讀者可以看清全部細節。

圖4-21 新的負載牽引原理圖

這里有以下兩點需要注意:

Freescale參考設計用于2500-2700MHz,需要改變四分之一波長線的長度;

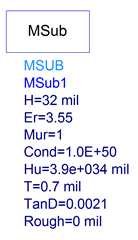

需要將所用PCB板材即Rogers RO4003C各項參數準確填寫于MSub模型中,如圖4-22。

圖4-22 將RO4003C各項參數填寫于MSub模型

按照圖4-21中的原理圖,重新進行負載牽引仿真,可以得到如圖4-23所示的仿真結果,可以看到m3處在50歐姆附近,可以獲得46.23dBm的輸出功率及55.3%的PAE,完全可以達到預期指標。

圖4-23 新的負載牽引仿真結果

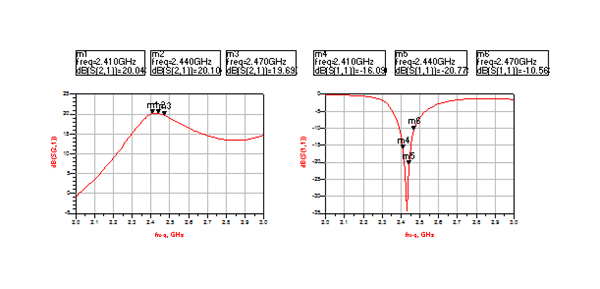

根據習慣,我們再進行一次S參數仿真,按照圖4-24繪制新的仿真原理圖,仿真后,可以得到如圖4-25所示的仿真結果。可以看到,在2.4GHz WiFi設備的頻率范圍內,這樣的匹配已經達到了很高的指標,S11全部在-10dB以下,增益也高達20dB左右,完全可以滿足本產品要求。

圖4-24 S參數仿真原理圖

圖4-25 S參數仿真結果

需要指出的是,S11的曲線過于尖銳,這可能是未來較大的風險所在,一旦PCB制作有偏差,那么最終的指標可能會差得比較多,不過作為第一版,還是值得做些嘗試。

4.2.7 制作LDMOS模塊

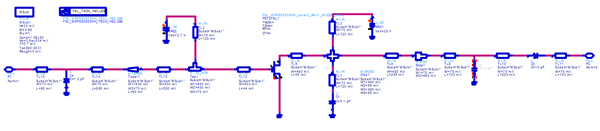

4.2.6中的仿真結果已經完全滿足要求,這時我們需要將4.2.6中的原理圖封裝成一個模塊,以便后續的聯合仿真。去除圖4-24中的S-PARAMETERS控件,并將Term1,Term2更換為Port1,Port2,如圖4-26所示。

圖4-26 制作MRF8S26060H模塊

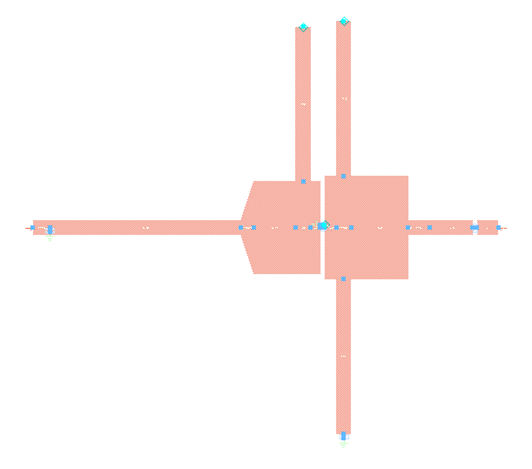

為了保證LDMOS模塊的準確性,我們使用ADS生成一下PCB,可以看到如圖4-27的效果,可以看到,與MRF8S26060的參考設計非常一致,只是四分之一波長走線未做轉彎處理。

圖4-27 LDMOS PCB圖

至此,我們已經完成LDMOS的全部仿真工作,在后續的聯合仿真中,直接調用本節中只做的模塊即可。

4.3 功分器設計與仿真

在4.2節中,我們已經得知單顆LDMOS可以達到46.23dBm的射頻輸出功率,這距離我們的目標值50dBm還有些差距,因此考慮使用兩顆LDMOS做功率合成,這就需要設計一個合適的功分器。

在MRF8S26060_Sim_prj工程下新建一份原理圖,點擊DesignGuide?Passive Circuit,如圖4-28所示。

圖4-28 使用DesignGuide中的Passive Circuit功能

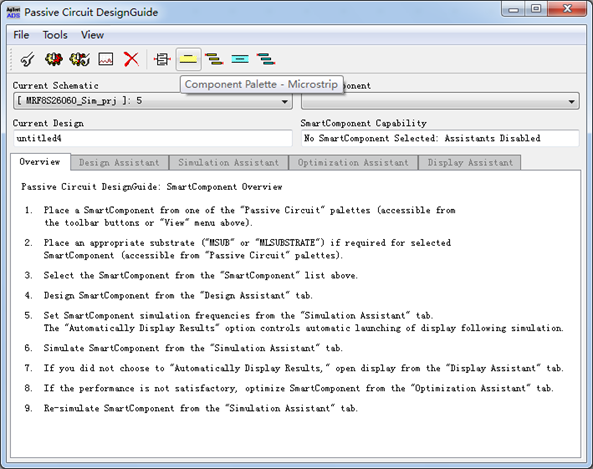

在彈出的對話框中點擊Component Palette – Microstrip圖標,如圖4-29所示。

圖4-29 點擊Component Palette – Microstrip圖標

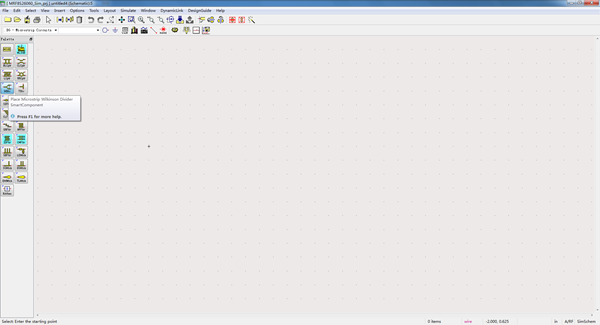

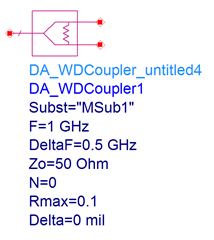

在更新的原理圖設計窗口中點擊Place Microstrip Wilkinson Divider按鈕,將Wilkinson功分器符號添加至原理圖中,如圖4-30所示。添加完成后的原理圖如圖4-31所示。

圖4-30 在原理圖中添加Wilkinson功分器

圖4-31 添加完成的Wilkinson功分器

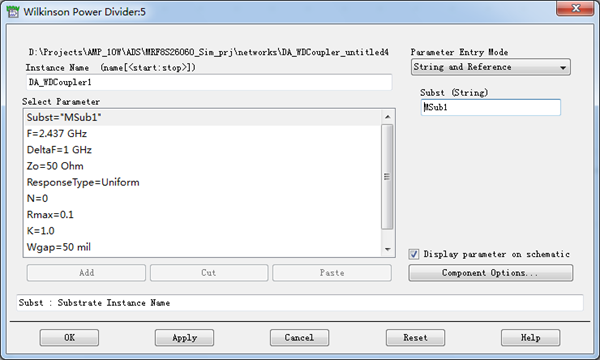

這時雙擊Wilkinson功分器符號,更改其目標參數,如圖4-32所示。

圖4-32 更改Wilkinson功分器參數

這時我們還需要為原理圖添加MSub模型,采用與4.2.6中所提到的模型一致即可。相信此時讀者能體會到我把PCB板材的選擇作為仿真最開始的內容進行講述,因為所有的仿真都離不開PCB參數。添加MSub模型后的原理圖如圖4-33所示。

圖4-33 添加MSub模型

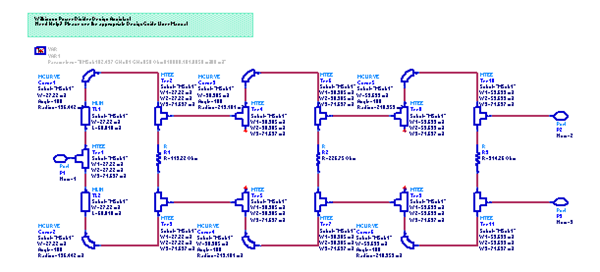

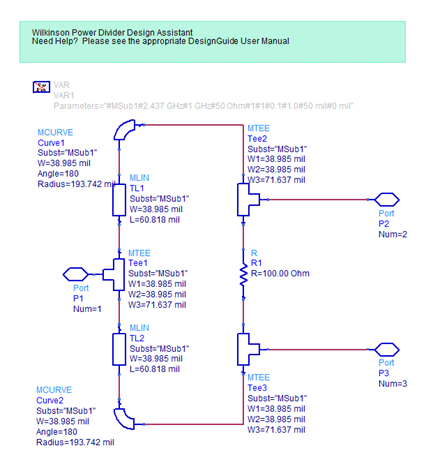

這時回到Passive Circuit DesignGuide對話框中,點擊Design Assistant標簽,ADS就會自動為我們設計完成一款合格的功分器,在DA_WDCoupler1_untitled4上面點擊Push Into Hierarchy之后,我們可以看到功分器的細節,如圖4-34所示。

圖4-34 功分器內部細節

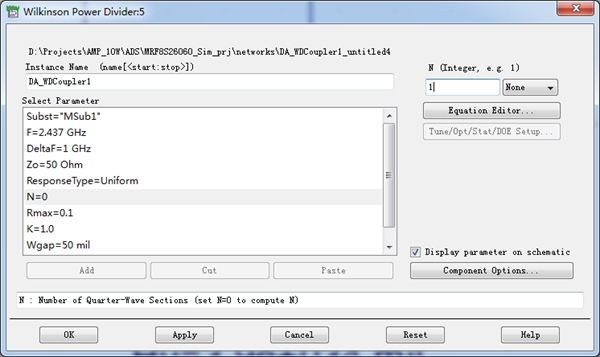

而易見的是,這樣的功分器尺寸太大,不方便在這個產品上使用。我們重新調整DA_WDCoupler1_untitled4的參數,如圖4-35所示。

圖4-35 調整Wilkinson功分器參數

再次點擊Passive Circuit DesignGuide對話框中的Design Assistant標簽,并在設計完成的功分器上點擊Push Into Hierarchy之后,我們可以看到新的功分器內部結構,如圖4-36所示。

圖4-36 新的功分器內部結構

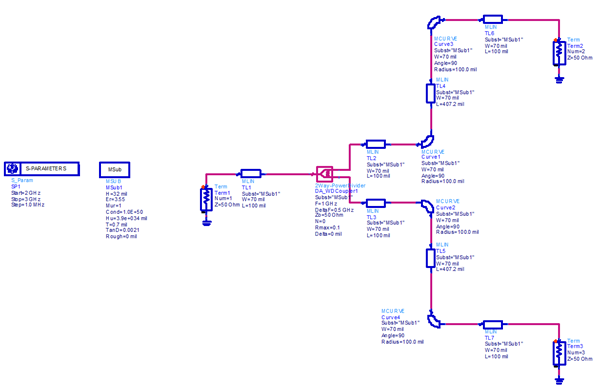

接下來對這個功分器進行S參數仿真,原理圖如4-37所示。

圖4-37 對功分器進行S參數仿真

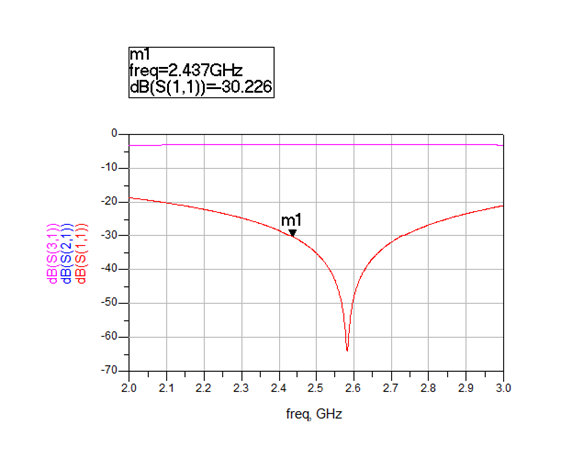

仿真后的結果如圖4-38所示,顯然,這個功分器完全可以達到我們的要求。

圖4-38 功分器仿真結果

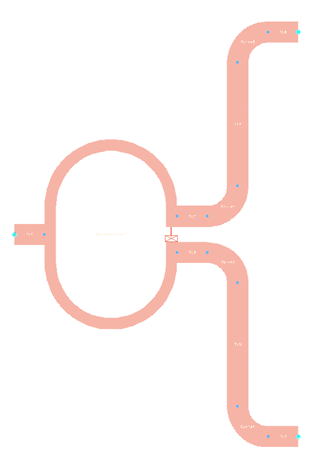

最后,將這個功分器生成PCB Layout,我們可以看到如圖4-39所示的結果。

圖4-39 功分器生成PCB Layout

也許這個時候讀者會有疑問,PCB設計使用的軟件是Cadence Allegro,如何將這個功分器輸入至Allegro呢?讀者不必著急,在無線時代后續的章節中,后面會講解到。

4.4 定向耦合器設計與仿真

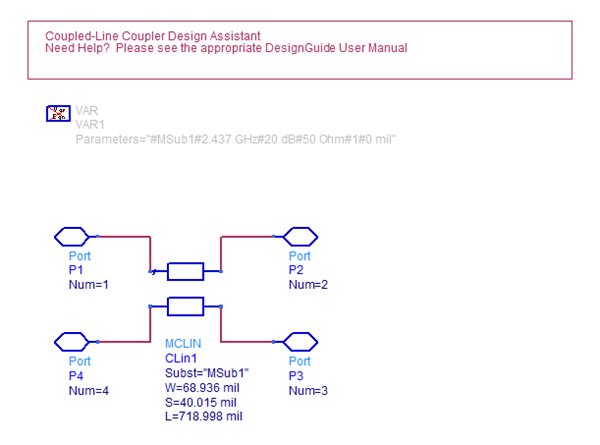

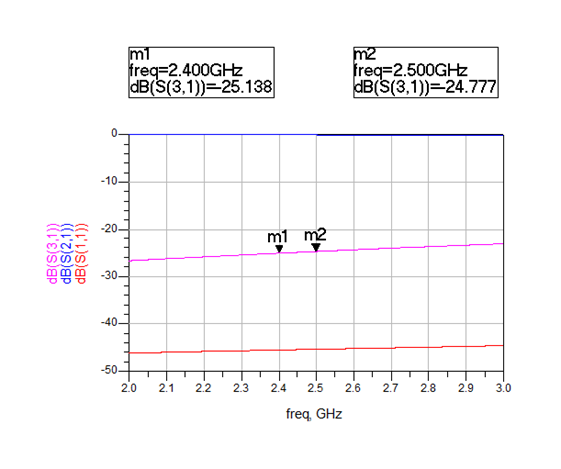

經過4.3的詳細講解,我相信讀者有能力自行完成定向耦合器的設計與仿真,兩者的過程十分類似,因此不再贅述,這里只給出最終的仿真和設計結果。

圖4-40 定向耦合器設計結果

圖4-41 定向耦合器仿真結果

圖4-42 定向耦合器PCB Layout

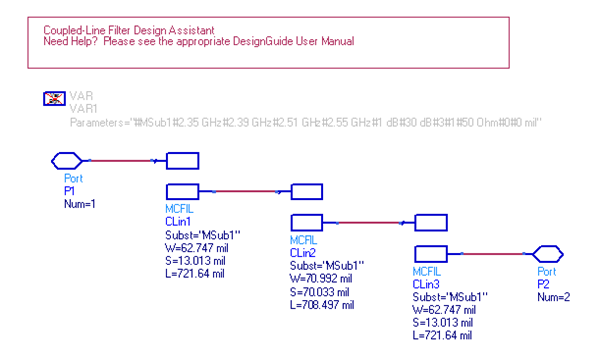

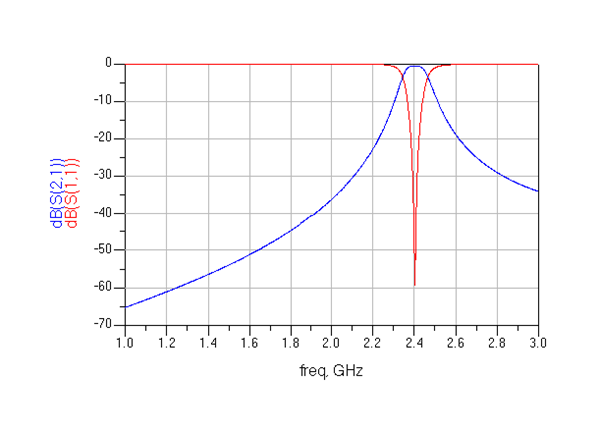

4.5 帶通濾波器設計與仿真

與定向耦合器類似,本節只給出帶通濾波器的仿真與設計結果。

圖4-43 帶通濾波器內部結構

圖4-44 帶通濾波器仿真結果

圖4-44 帶通濾波器仿真結果

圖4-45 帶通濾波器PCB Layout

下一篇: PLC、DCS、FCS三大控

上一篇: Allegro中如何導入Out