結(jié)合數(shù)字式頻率合成器(DDs)和集成鎖相環(huán)(PLL)各自的優(yōu)點,研制并設(shè)計了以DDS芯片AD9954和集成鎖相芯片ADF4113構(gòu)成的高分 辨率、低雜散、寬頻段頻率合成器,并對該頻率合成器進行了分析和仿真,從仿真和測試結(jié)果看,該頻率合成器達到了設(shè)計目標。該頻率合成器的輸出頻率范圍為 594~999MHz,頻率步進為5Hz,相位噪聲為-91dBc。

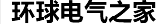

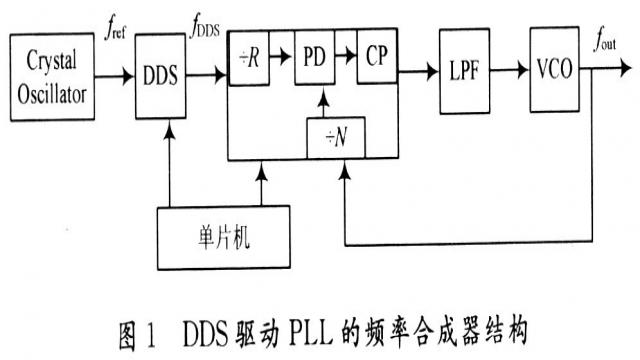

DDS的參考信號由晶振產(chǎn)生,其頻率為fref。DDS輸出的信號頻率為fDDS,頻率值由頻率控制字(FTW)控制。鎖相環(huán)(PLL)的參考信號由 DDS的輸出信號驅(qū)動。VCO的輸出頻率由PLL芯片的電荷泵(CP)輸出,并通過低通濾波器(LPF)后控制。頻率合成器的輸出信號為VCO的輸出信 號。該頻率合成器通過單片機提供控制信號,以改變DDS中FTW和PLL的分頻比。

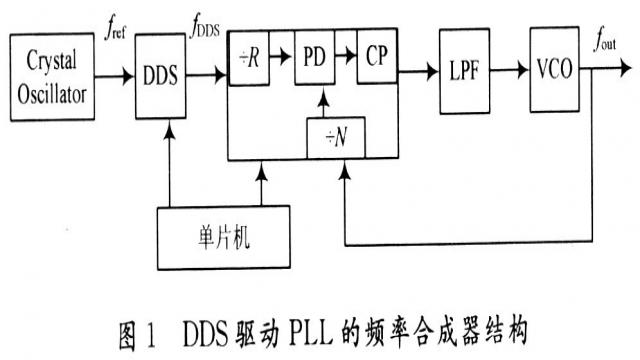

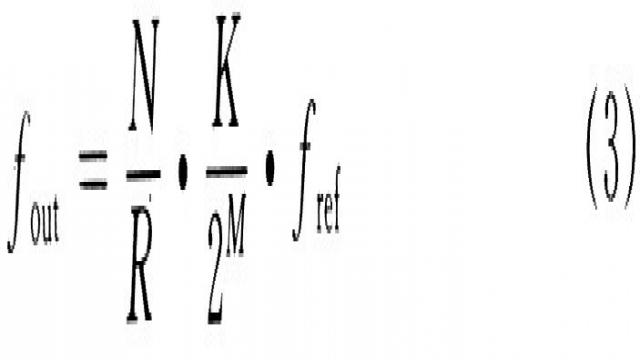

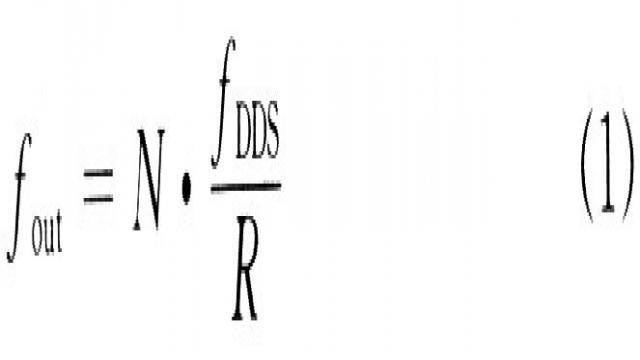

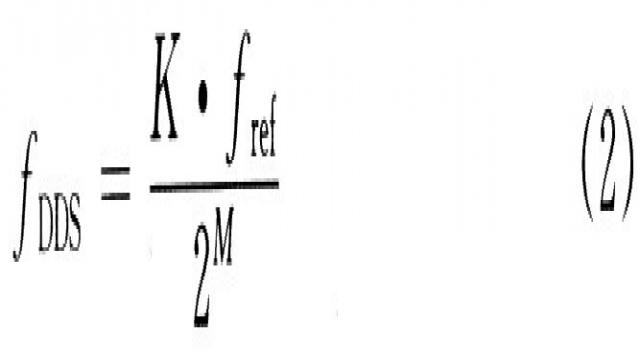

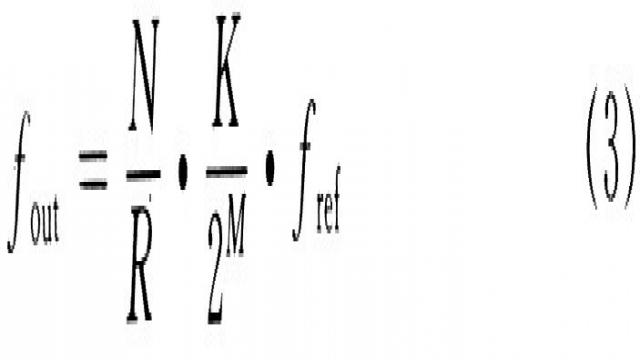

VCO輸出信號頻率與DDS輸出信號頻率間的關(guān)系為:

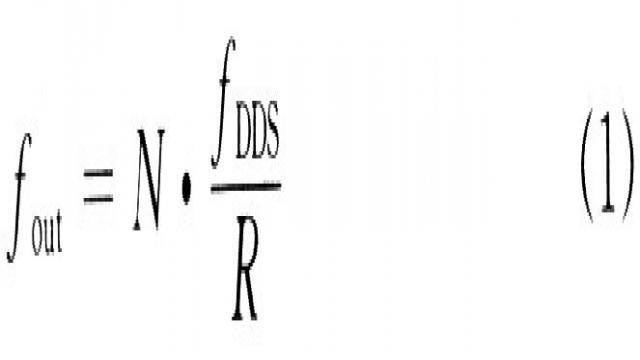

而DDS的輸出頻率由頻率控制字K控制,且有:

式中:M是DDS的相位累加器的位數(shù);fref是DDS的內(nèi)部時鐘。這樣,式(1)可以寫成:

在圖1所示的結(jié)構(gòu)中,由于DDS模塊具有較高的頻率分辨率,所以從式(3)可以看出,理論上輸出信號具有比傳統(tǒng)結(jié)構(gòu)更高的頻率分辨率。設(shè)計中晶振頻率為 400MHz,PLL分頻比為27。由式(3)計算可知,該頻率源可以實現(xiàn)5Hz的頻率分辨率。其中DDS的輸出頻率為22~37MHz,所以系統(tǒng)輸出頻 率范圍為594~999MHz,達到了設(shè)計要求。

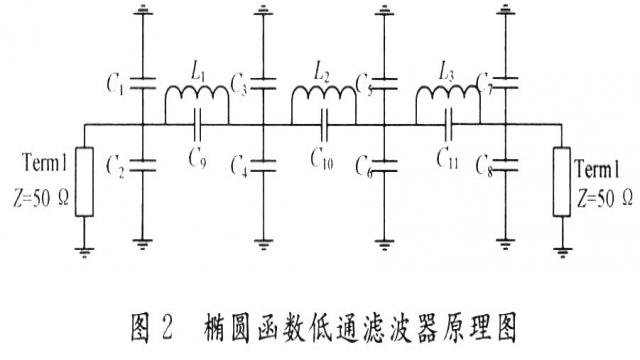

1.2 電路實現(xiàn)

對于DDS模 塊,采用了AD9954芯片產(chǎn)生低頻參考信號。AD9954是ADI公司最新的AgiIeRF合成器,具有32位的頻率控制字。在400MHz的時鐘頻率 下,輸出頻率分辨率可以達到約4.7×10-5Hz,具有14位可編程移相單元。芯片采用了先進的:DDS技術(shù),內(nèi)部集成14位的高性能DAC。該DAC 具備優(yōu)秀的動態(tài)性能,相位噪聲優(yōu)于-120dBc/

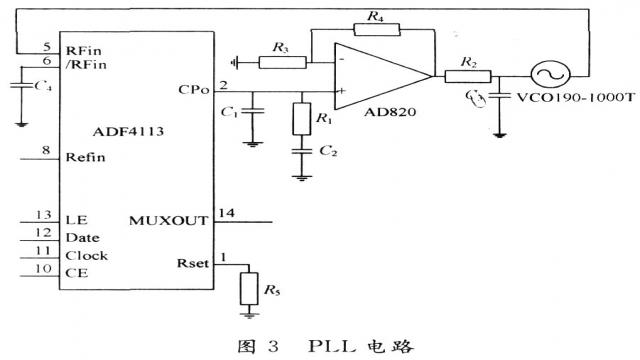

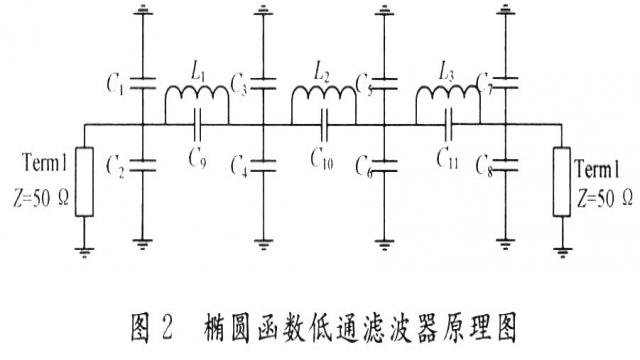

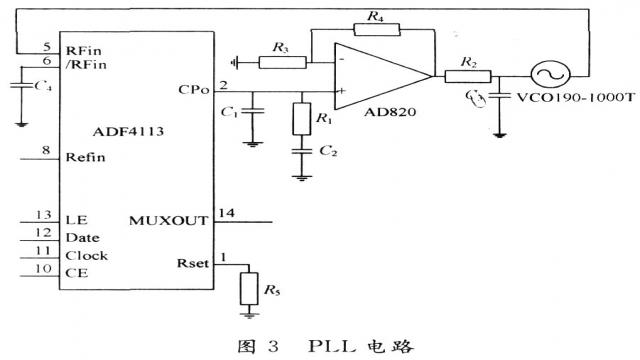

PLL模塊在該設(shè)計結(jié)構(gòu)中尤為重要。在此采用ADF4113鎖相環(huán)芯片。ADI公司研制的數(shù)字鎖相頻率合成器ADF4113,最高工作頻率可達 4GHz,主要應(yīng)用于無線射頻領(lǐng)域,用以構(gòu)成數(shù)字鎖相環(huán),鎖定某一頻率。該電路內(nèi)部資源主要包括可編程的模分頻 器:8/9,16/17,3z/33,64/65;可編程的14位參考頻率分頻器;可編程的射頻信號分頻器;3線串行總線接口;模擬和數(shù)字的鎖定狀態(tài)檢測 功能。該芯片的最高鑒相頻率達到55MHz,芯片的底噪為-171dBc/

2 電路分析與仿真

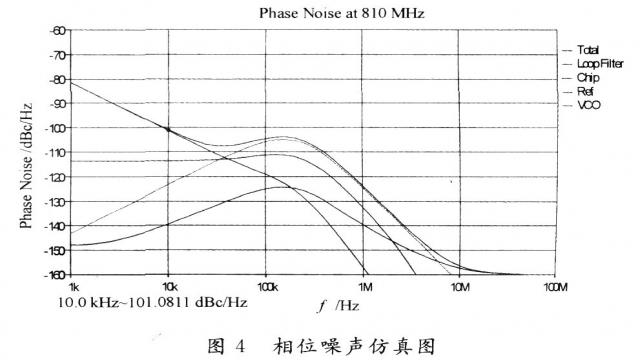

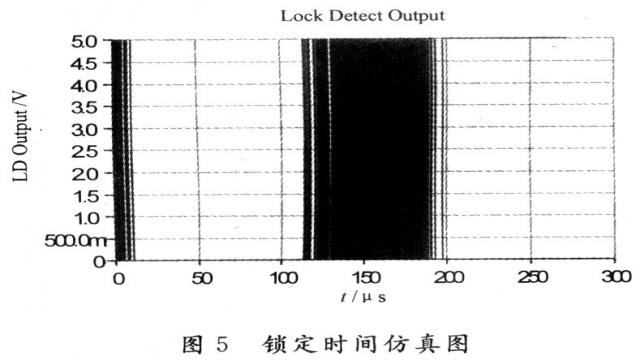

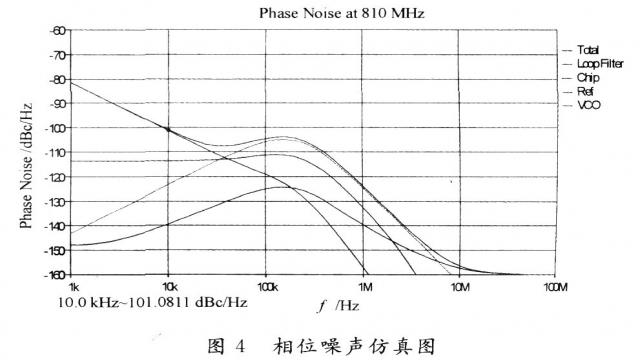

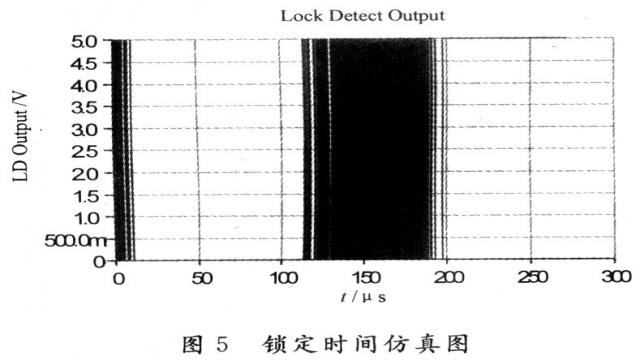

為了分析和評估提出的頻率綜合器性能,采用ADISimPLL軟件對該方案的相位噪聲模擬仿真。仿真結(jié)果如圖4,圖5所示。這里給出頻率為810MHz,環(huán)路帶寬為120kHz的相位噪聲仿真圖形以及鎖定時間圖形,從圖中可以看出,該方案滿足了設(shè)計目標的要求。

3 實驗及測量結(jié)果

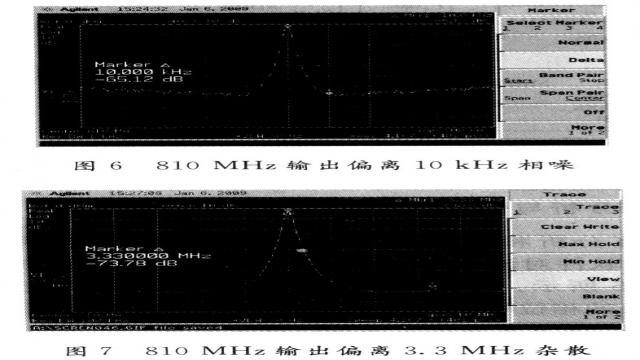

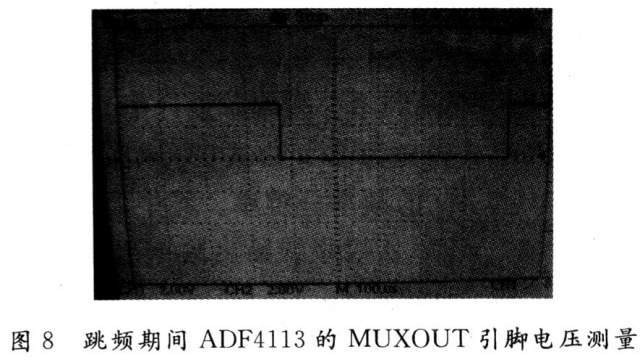

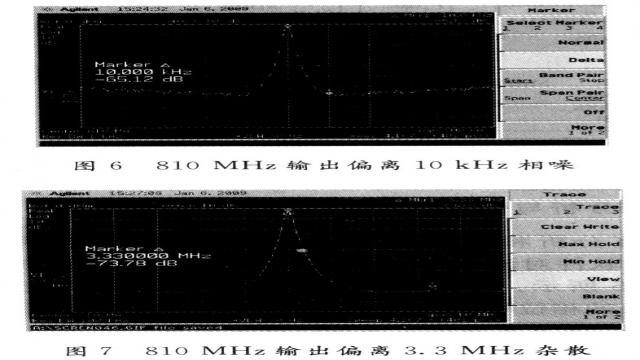

為了檢驗文中給出的頻率綜合器性能,使用Agi-lentE4401B對掃頻源的相位噪聲、雜散進行測量,測量結(jié)果如圖6~圖8所示。 594~999MHz包含了很多頻點,測試時選擇了一系列較有代表性的點進行測量,限于篇幅,這里給出810MHz頻點相位噪聲和雜散的測量結(jié)果。由圖可 見,相噪為-92dBc/

4 結(jié)語

介紹了一種采用DDS激勵PLL的頻率合成器,有效地克服了寬帶系統(tǒng)中DDS輸出頻率較低和PLL頻率分辨率低的缺點。取長補短實現(xiàn)頻率合成,實現(xiàn)了單一技術(shù)難以達到的效果。